Scendere in dimensioni dei transistors porta a tutta una serie di sfide quando si disegnano i core e tutto ciò che li circonda. Anche ignorando i requisiti di corrente e le frequenze di funzionamento, la sola abilità nel creare qualcosa di così piccolo e “stamparlo” nel silicio, e di integrare tale silicio in un package, mentre si fornisce corrente ad esso, è un vero e proprio ostacolo da superare.

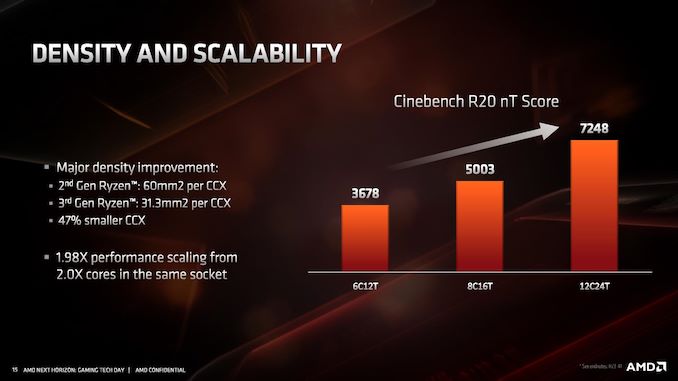

Un’unità di paragone fornita da AMD si collega al CCX: 4 core, la relativa struttura hardware e le cache L2 e L3. Con il processo a 12 nm di Zen+, AMD ha affermato che un singolo CCX occupava circa 60 mm², divisi in 44 mm² per i core e 16 mm² per gli 8 MB di cache L3. Addizionate due di questi CCX ad un controller di memoria, alle linee PCIe, ai link Infinity Fabric e al resto dell’I/O, ed ecco che le dimensioni totali di un die Zen+ raggiungevano un totale di 213 mm².

Con Zen 2, un singolo chiplet è grande 74 mm², di cui circa 31.3 mm² sono occupati dal CCX con 16 MB di cache L3.

AMD non ha specificato quanto dei 31.3 mm² sia occupato dalla cache, ma vista la dimensione ben maggiore rispetto alla generazione precedente, si può ricavare che sia quasi metà del totale. La ragione per cui un die di Zen 2 sia così piccolo è da ricercarsi nel fatto che il chiplet non richiede un memory controller, richiede un singolo link Infinity Fabric e non ha I/O, visto che tutti questi requisiti sono gestiti dal die centrale I/O dedicato.

Ciò consente ad AMD di creare chiplets estremamente compatti.

Per capirci, AMD ha dichiarato che un CCX (core e cache L3) ha visto le sue dimensioni diminuire del 47% circa. Ciò significa un aumento repentino della densità di potena di calcolo, specie se si tiene in considerazione l’aumento del 15% di IPC dichiarato e le maggiori frequenze di funzionamento.

Discussione su post